mcmaster:northern-telecom:t36a

This is an old revision of the document!

Dual integrating sigma-delta ADC/DAC

NorTel CMOS41S process, 1.2 micron, double metal, double poly spec'ed clock rate is 10.24 MHz funtion is to test a double integration sigma delta modulated ADC and DAC analog switched capacitor filters on front end digital logic does decimation on ADC path and interpolation on DAC path

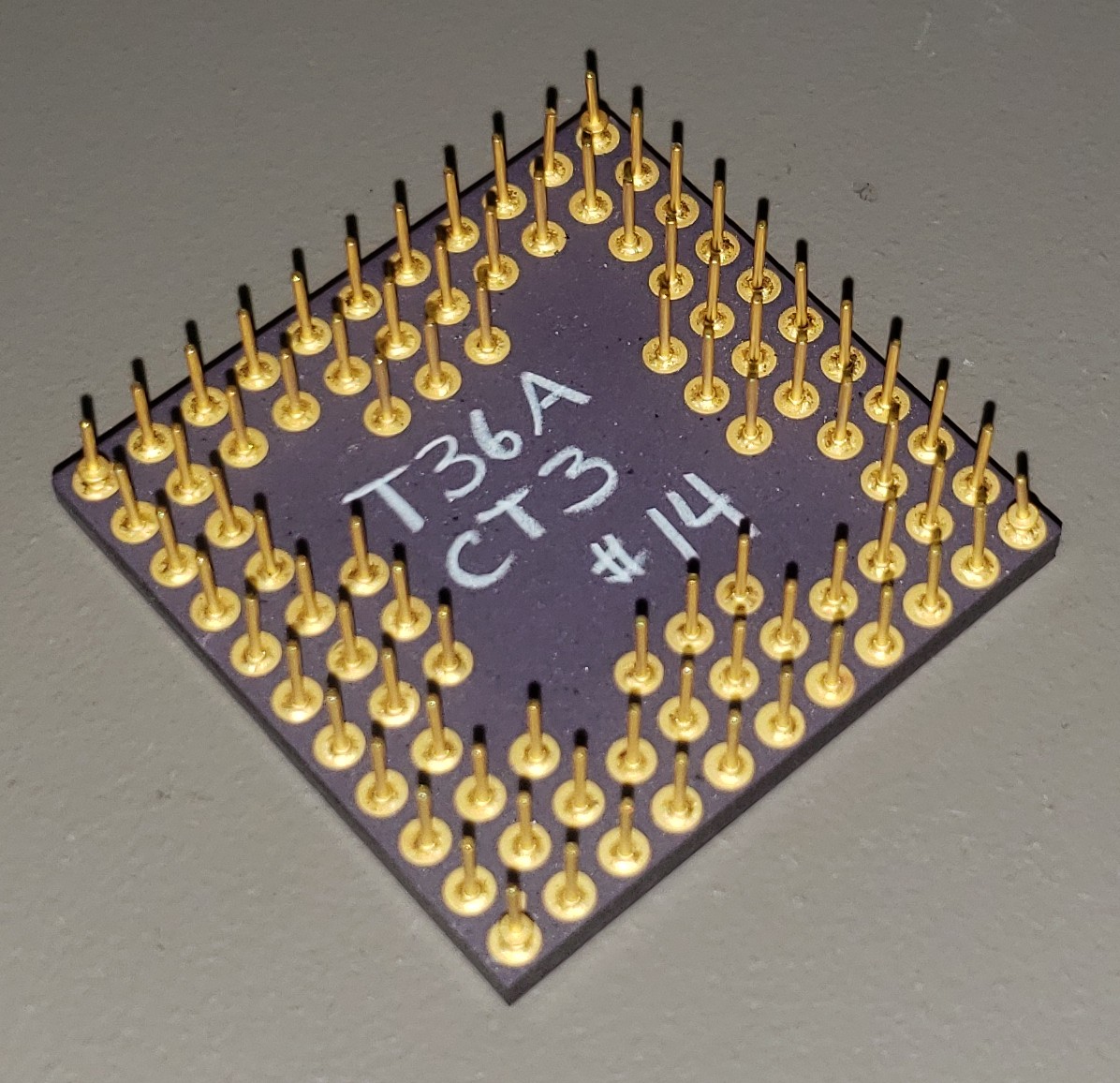

Package

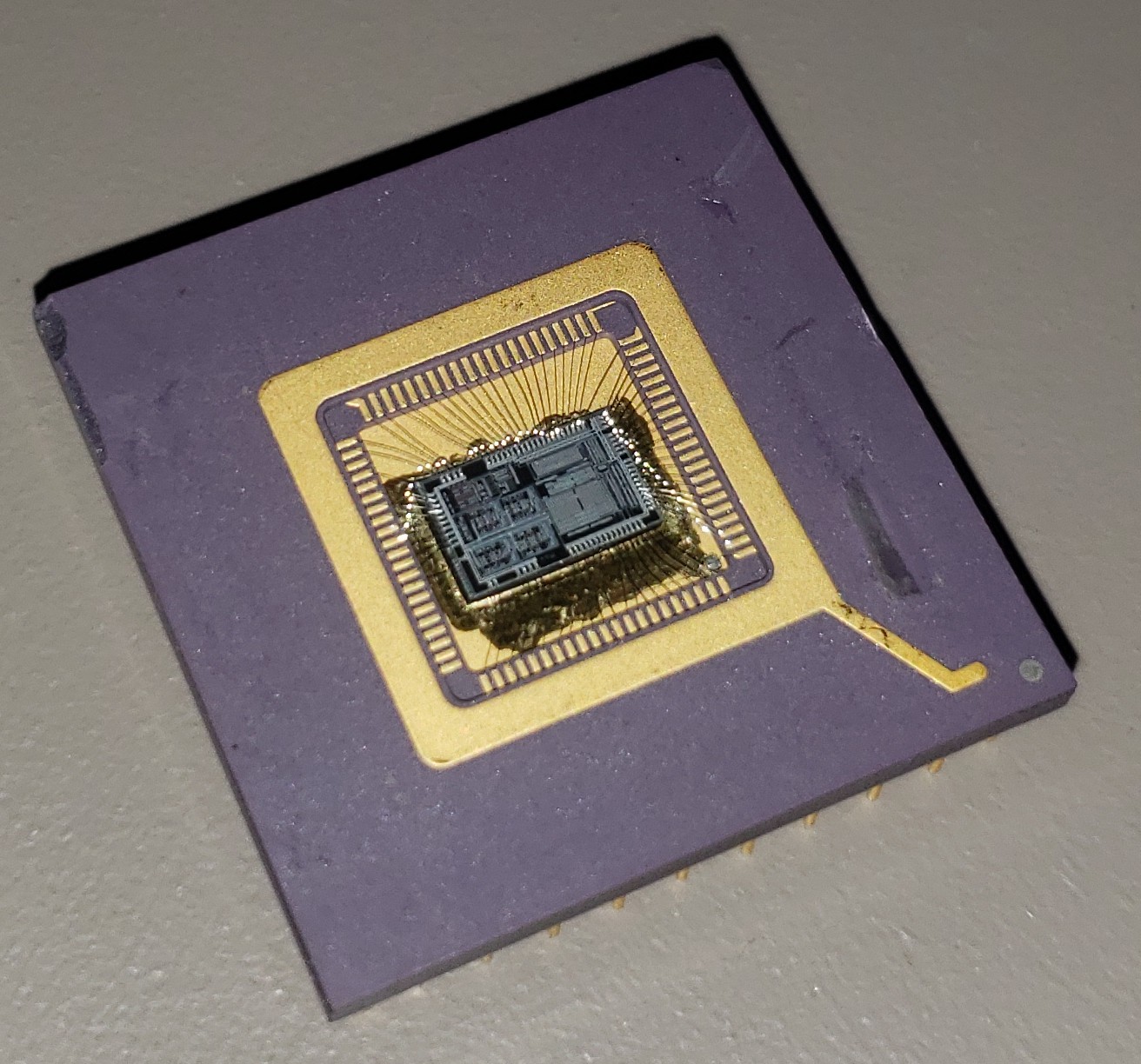

Die

mcmaster/northern-telecom/t36a.1640950218.txt.gz · Last modified: 2021/12/31 11:30 by cr1901