rsa:securid:sid700

Table of Contents

Gray SecurID

Images

Die markings

SMSC 2C 2C 2C5737 18A -1P89

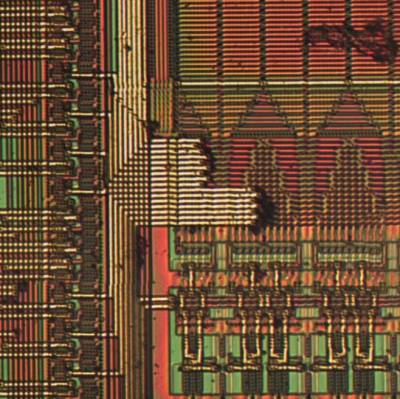

Chip structure

Die is approximately 2.9 X 3.1 mm

Process technology

2-metal nonplanar CMOS, fairly large dimensions (1um? 750nm?). Based on standard cells with approximately 16 horizontal interconnect channels on M1 between rows of cells and vertical interconnect on M2.

CPU

12 rows of standard cells, no estimates of total gate count yet.

Based on memory architecture it's likely a 16 bit design.

Memory

First array (top center, red)

- Best guess so far is mask ROM

- Two identical banks with column addressing circuitry in the middle, row addressing at right

- Each bank consists of 128 rows

- Data bus at center left is 16 bits wide

- Probable structure: 16 bits x 256 rows = 4k bits

Closeup of column outputs. Looks like 16 data bits.

Second array (top left, gray)

- Best guess so far is SRAM

- One bank with column addressing circuitry on top and row addressing circuitry at left

- 16 columns, 64 rows

- Probable structure: 16 bits x 64 rows = 1k bits

Current issue SID700

rsa/securid/sid700.txt · Last modified: 2025/08/04 21:24 by 127.0.0.1